Dans quels buts les attaques par canal auxiliaire peuvent être menées ?

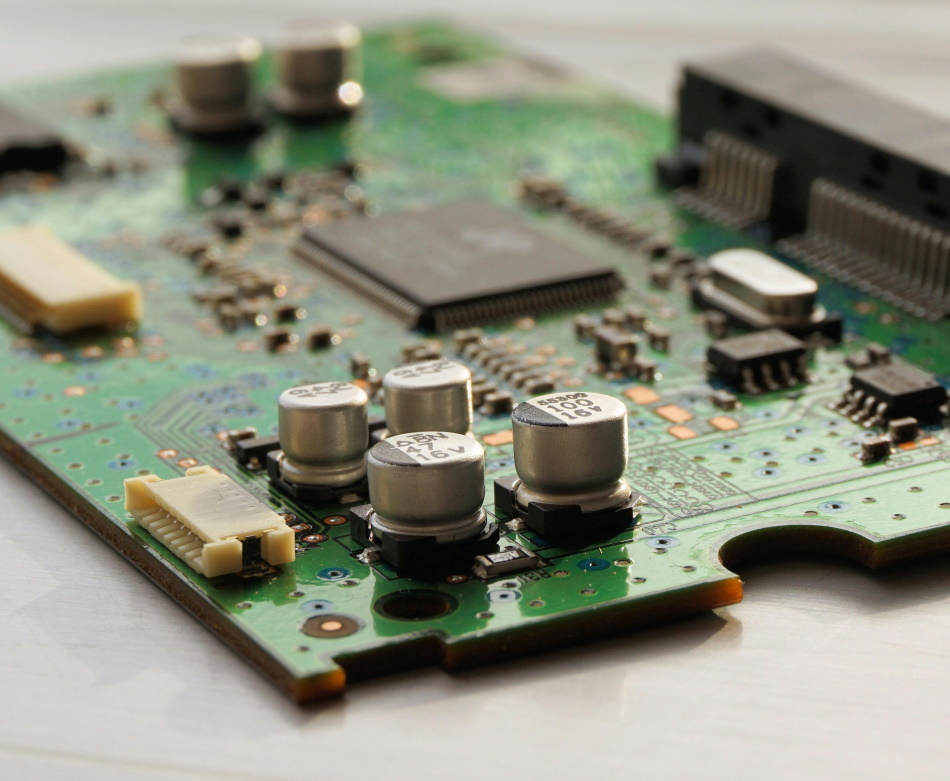

Maria Mushtaq : Une attaque par canal auxiliaire vise à recueillir des informations ou à influencer l’exécution d’un programme en exploitant les failles d’un système. C’est le matériel informatique (hardware) qui est visé, plutôt que d’exploiter les failles dans le code d’un logiciel. Les dernières failles de sécurité informatiques telles que Spectre et Meltdown, ainsi qu’un grand nombre d’offensives, ont montré que les attaques par canal auxiliaire sont très puissantes. En quelques microsecondes, un attaquant peut prendre le contrôle d’un système informatique entier.

Quelles sont les conséquences de ces attaques sur la société ?

MM : Aujourd’hui les attaques par canal auxiliaire peuvent être observées sur toutes les composantes d’une architecture informatique : sur des interfaces de stockage, des applications, des systèmes d’exploitations et sur la microarchitecture. Cette tendance s’accentue et la surface d’attaque complète n’est pas encore connue. À l’échelle de la société, les attaques par canal auxiliaire peuvent causer des blackouts d’électricité ainsi que des dommages sur des équipements militaires et nucléaires. Des données médicales et secrètes peuvent aussi être récoltées grâce à ce type d’attaque.

Qu’est-ce qui permet le déploiement des attaques par canal auxiliaire ?

MM : Ces attaques exploitent des vulnérabilités qui sont en fait profondément liées à l’architecture des processeurs. Je pense que la raison fondamentale de l’existence de ces vulnérabilités est que l’évolution de l’informatique a jusqu’à aujourd’hui principalement porté sur l’accroissement des performances informatiques. La sécurité a souvent été pensée après coup et pas au moment de la conception du hardware.

Comment fonctionne une attaque par canal auxiliaire ?

MM : D’une manière générale, l’attaque par canal auxiliaire exploite des failles résultantes de l’implémentation d’un matériel ou d’un logiciel. Par exemple si nous parlons des attaques récemment découvertes, Spectre et Meltdown, elles manipulent l’exécution spéculative pour modifier l’état du microprocesseur. Les processeurs modernes utilisent l’exécution spéculative pour anticiper le lancement d’une opération de calcul, au cas où il ait besoin d’être exécuté, mais sans que cela soit nécessaire (cela leur permet d’améliorer leurs performances). En d’autres termes, les CPU essaient d’anticiper les actions qui vont être demandées. Lorsque la valeur mémoire arrive, le CPU rejette ou engage le calcul spéculatif. L’attaquant peut accéder à la mémoire et aux registres (blocs de mémoire contenant des données destinées à être utilisées immédiatement ou à très court terme) de la victime.

L’attaque Meltdown contourne quant à elle l’isolation de la mémoire. Elle utilise des canaux auxiliaires pour récupérer les données des caches qui sont introduites dans les registres et les caches non validés en raison de la génération d’une exception. Cette dernière permet à l’attaquant d’accéder de façon non autorisée à une zone de la mémoire.

Où en est la recherche sur la sécurité micro-architecturale pour répondre à ces menaces ?

MM : En tant que sujet de recherche, la sécurité micro-architecturale a débuté suite à la découverte de quelques vulnérabilités qui peuvent être trouvées dans presque tous les processeurs modernes. Il a été démontré que plusieurs attaques exploitent ces vulnérabilités et permettent de faire fuir des données sensibles telles que des mots de passe ou toute autre information secrète stockée sur un ordinateur. Avec l’essor du calcul informatique dans le cloud, cela constitue une véritable menace, puisque les infrastructures de cloud computing centralisent les données sensibles de nombreux acteurs. De plus, il n’y a pour le moment pas de solution simple pour remédier à ce problème. Aujourd’hui nous sommes toujours à la recherche de moyens efficaces pour détecter et éviter des attaques micro-architecturales. C’est justement la recherche et le développement de solutions pour les futures générations de processeurs qui m’a motivé à travailler sur ces sujets.

Pourquoi est-il si difficile de se protéger contre ce type d’attaque ?

MM : Les pratiques en matières d’attaques par canal auxiliaire ont démontré que presque tout, dans les processeurs actuels, peut être attaqué, et qu’il n’est pas possible d’établir une sécurité fiable à 100 %. Pour développer des processeurs sécurisés, il est important d’étudier les différents modèles de menaces puisque les attaques par canal auxiliaire sont de diverses natures. Des protections uniques ne peuvent pas être assurées pour tous les types de vulnérabilité. Par ailleurs, il est important de travailler sur la sécurité des processeurs tout en évitant de leur faire perdre la performance qu’ils ont pu gagner au cours des décennies.

Concrètement, quelles sont les pistes envisagées pour sécuriser les processeurs ?

MM : Le concept d’environnement d’exécution de confiance (TEE) prend une importance significative dans les approches modernes de conception de la sécurité. Par rapport aux niveaux de privilèges (autorisation d’exécuter une action accordée par un programme à un utilisateur) conventionnels, le concept de TEE permet une meilleure gestion des privilèges logiciels. Toutefois, les solutions basées sur le TEE soulèvent deux problèmes majeurs. D’une part, elles reposent toujours sur le principe du renforcement de l’isolation en fournissant une zone sécurisée du processeur principal pour assurer la sécurité de bout en bout en protégeant l’exécution du code authentifié. Par conséquent, le coût de la confidentialité, de l’authenticité, du respect de la vie privée, de l’intégrité du système et des droits d’accès aux données dans le cadre du TEE est toujours payé en termes de dégradation des performances. D’autre part, des recherches récentes ont indiqué que les conceptions basées sur TEE, comme le SGX d’Intel et le Truszone d’ARM, sont vulnérables à de nouveaux vecteurs d’attaque. Par ailleurs, l’architecture RISC V pour les microprocesseurs est une excellente initiative open-source qui intègre la sécurité comme caractéristique de conception. Les chercheurs ont toutefois fourni des modèles de fuite d’informations pour RISC V.

Les recherches devraient se concentrer sur une méthodologie à deux volets pour répondre aux problèmes de sécurité dans les futurs systèmes informatiques. À court terme, il est essentiel de travailler à trouver un équilibre entre les exigences de performance et la sécurité. À long terme, il est nécessaire de travailler à proposer de nouvelles approches qui aideront à incorporer la sécurité comme une caractéristique de conception à travers de multiples niveaux de la pile informatique.